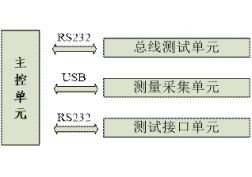

图11. 倾斜补偿器方案

倾斜补偿器对信号进行整形,并且在通过功率放大器处理信号时保持整形轮廓。传统数字预失方案会将整形视为减损并尝试针对其进行校正,因为数字预失真是(非线性)均衡器。似乎合理的是,如果将倾斜的倒数添加到观测路径中,就可以减轻其影响。但事实并非如此。功率放大器是非线性的,因此交换性不适用,也就是说:

PA 代表功率放大器;T代表倾斜补偿器

为了实现最佳操作,数字预失真处理模块需要明确了解在功率放大器输入端处显示的信号。在电缆数字预失真应用中,利用数字预失真算法为功率放大器建模的同时,必须保持倾斜补偿。这就会面临一些非常独特和极具难度的挑战。我们需要一个稳定的低成本解决方案,不会使倾斜均衡。虽然无法在本文中披露该解决方案的性质,但ADI已经找到了一个创新的解决方案,将在未来的出版物中详细介绍。

数字预失真和电缆功率放大器架构

如图4所示,典型的电缆应用将把一个DAC的输出分成四路并提供给四个独立的功率放大器。为了最大程度节省功率,需要在所有这些功率放大器上实施数字预失真。可行的解决方案可能是实施四个独立的数字预失真模块和DAC模块。该解决方案有效,但会使效率降低,系统实施成本增加。额外的硬件需要资金和功率成本。

并非所有功率放大器都是一样的,尽管工艺匹配(制造过程中)可以提供具有相似个性的单元,但差异仍会存在,并且随着老化、温度和供电波动而变大。然而,将一个功率放大器用作主机并为其开发优化的数字预失真,然后将其应用于其他功率放大器,确实可提供系统性能优势,如图12中的仿真结果所示。

左侧的曲线表示未采用数字预失真情况下的功率放大器性能。非线性工作模式导致失真,这体现在MER1性能(范围为37 dBc至42 dBc)中。闭环数字预失真应用于观测主功率放大器的输出;曲线图右侧的绿色曲线表示的是增强性能。数字预失真已针对功率放大器失真进行了校正,结果是总体性能经过转变后可提供65 dBc到67 dBc的MER。图中间剩余的曲线表示的是从功率放大器的性能,即根据主功率放大器进行校正的功率放大器。可以看出,只观测一个功率放大器来实施闭环数字预失真可使所有功率放大器的性能受益。然而,从功率放大器仍然存在会失效的工作点。从功率放大器的性能范围从38 dBc到67 dBc。宽范围本身不是问题,但该范围的一部分低于可接受的工作阈值(电缆通常为45 dBc)。

图12. 使用多个功率放大器的单次数字预失真(仿真结果)

电缆中独特的系统架构为数字预失真提供了额外挑战。优化性能需要采用闭环数字预失真方案。但根据惯性思维,在电缆中这样做将需要在每个功率放大器路径中附加硬件。最佳解决方案需要 为每个功率放大器提供闭环数字预失真的增强功能,但不需要额外的硬件成本。

利用SMART算法解决挑战

如本文之前所述,电缆数字预失真为设计人员带来了非常独特和 具难度的挑战。如果在功率和硬件的限制范围内解决这些挑战,那么优势就不会被削弱;如果把功率放大器中节省下来的功率用于额外的DAC或FPGA,则对于功率放大器省电几乎没有任何价值。同样地,省电必须与硬件成本平衡。ADI通过结合高性能模拟信号处理与先进算法方案解决了该挑战。

ADI方案的高级概述如图13所示。该解决方案可以被认为具有三个关键要素:使用高级转换器和定时产品、采用支持全面信号链监控/控制的架构、运用可利用已有知识实现最佳性能的数字预失真先进算法。