图1. 采样保持拓扑结构:(1a) 单列,(1b) 双列。

延迟映射THA和ADC

开发采样保持器和ADC信号链的最困难任务之一,是在THA捕获采样事件的时刻与应将其移到ADC上以对该事件重新采样的时刻之 间设置适当的时序延迟。设置两个高效采样系统之间的理想时间差的过程被称为延迟映射。

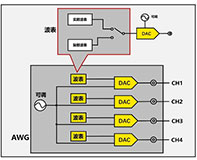

在电路板上完成该过程可能冗长乏味,因为纸面分析可能不会考虑PCB板上时钟走线传播间隔造成的相应延迟,内部器件组延迟,ADC孔径延迟,以及将时钟分为两个不同段所涉及到的相关电路(一条时钟走线用于THA,另一条时钟走线用于ADC)。设置THA和ADC之间延迟的一种方法是使用可变延迟线。这些器件可以是有源或无源的,目的是正确对准THA采样过程的时间并将其交给ADC进行采样。这保证了ADC对THA输出波形的稳定保持模式部分进行采样,从而准确表示输入信号。

如图2所示, HMC856 可用来启动该延迟。它是一款5位QFN封装,90 ps的固有延迟,步进为3 ps或25ps ,32位的高速延时器。它的缺点是要设定/遍历每个延迟设置。要使能新的延迟设置,HMC856上的每个位/引脚都需要拉至负电压。因此,通过焊接下拉电阻在32种组合中找到最佳延迟设置会是一项繁琐的任务,为了解决这个问题,ADI使用串行控制的SPST开关和板外微处理器来帮助更快完成延迟设置过程。

图2. 延迟映射电路。

为了获得最佳延迟设置,将一个信号施加于THA和ADC组合,该信号应在ADC带宽范围之外。本例中,我们选择一个约10 GHz的信号,并施加-6 dBFS的电平(在FFT显示屏上捕获)。延迟设置现在以二 进制步进方式扫描,信号的电平和频率保持恒定。在扫描过程中显示并捕获FFT,收集每个延迟设置对应的基波功率和无杂散动态范围 (SFDR) 数值。

结果如图3a所示,基波功率、SFDR和SNR将随所应用的每个设置而变化。如图所示,当把采样位置放在更好的地方(THA将样本送至ADC的过程之中)时,基波功率将处于最高水平,而SFDR应处于最佳性能(即最低)。图3b为延迟映射扫描的放大视图,延迟设定点为671,即延迟应该保持固定于此窗口/位置。请记住,延迟映射程序仅对系统的相关采样频率有效,如果设计需要不同的采样时钟,则需要重新扫描。本例中,采样频率为4 GHz,这是该信号链中使用的THA器件的最高采样频率。