图3b. 每个延迟设置上信号幅度和SFDR性能的映射结果(放大)。

针对大量原始模拟带宽的前端设计

首先,如果应用的关键目标是处理10 GHz的带宽,我们显然应考虑RF方式。请注意,ADC仍然是电压型器件,不会考虑功率。这种情况下,"匹配"这个词应该谨慎使用。我们发现,让一个转换器前端在每个频率都与100 MSPS转换器匹配几乎是不可能的;高频率带宽的RF ADC不会有太大的不同,但挑战依旧。术语"匹配"应表示在前端设计中能产生最佳结果的优化。这是一个无所不包的术语,其中,输入阻抗、交流性能 (SNR/SFDR)、信号驱动强度或输入驱动、带宽以及通带平坦度,这些指标都能产生该特定应用的最佳结果。

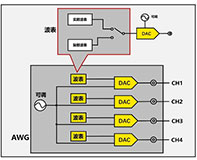

最终,这些参数共同定义了系统应用的匹配性能。开始宽带前端设计时,布局可能是关键,同时应当最大限度地减少器件数量,以降低两个相邻IC之间的损耗。为了达到最佳性能,这两方面均非常重要。将模拟输入网络连接在一起时务必小心。走线长度以及匹配是最重要的,还应尽量减少过孔数量,如图4所示。

图4. THA和ADC布局。

信号通过差分模式连接到THA输入(我们同时是也提供单端射频信号输入的参考设计链路),形成单一前端网络。为了最大限度地减少过孔数量和总长度,我们在这里特别小心,让过孔不经过这两条模拟输入路径,并且帮助抵消走线连接中的任何线脚。

最终的设计相当简单,只需要注意几点,如图5所示。所使用的0.01 F电容是宽带类型,有助于在较宽频率范围内保持阻抗平坦。典型的成品型0.1 F电容无法提供平坦的阻抗响应,通常会在通带平坦度响应中引起较多纹波。THA输出端和ADC输入端的5和10串联电阻,有助于减少THA输出的峰化,并最大限度地降低ADC自身内部采样电容网络的残余电荷注入造成的失真。然而,这些值需要谨慎地选择,否则会增加信号衰减并迫使THA提高驱动强度,或者设计可能无法利用ADC的全部量程。

最后讨论差分分流端接。当将两个或更多转换器连接在一起时,这点至关重要。通常,轻型负载(例如输入端有1 k负载)有助于保持线性并牵制混响频率。分流器的120 分流负载也有此作用,但会产生更多实际负载,本例中为50 ,这正是THA希望看到并进行优化的负载。

图5. THA和ADC前端网络及信号链。

现在看结果!检查图6中的信噪比或SNR,可以看出在15 GHz范围上可以实现8位的ENOB(有效位数)。这是相当不错的,想想对于相同性能的13 GHz示波器,您可能支付了12万美元。当频率向L、S、C和X波段移动时,集成带宽(即噪声)和抖动限制开始变得显著,因此我们看到性能出现滚降。

还应注意,为了保持THA和ADC之间的电平恒定,ADC的满量程输入通过SPI寄存器内部更改为1.0 V p-p。这有助于将THA保持在线性区域内,因为其最大输出为1.0 V p-p差分。