近日来,串扰测试话题热度持续,各工程师都在寻找相关的串扰测试方案,前些时日,中星联华科(北京)有限公司发布了《【有料干货】串扰测试方案(上篇)》,许多工程师纷纷留言期待下篇。

现在,下篇终于来了,快来看看中星联华科技(北京)有限公司给我们带来了什么样的串扰测试方案吧。

首先,我们先来看看上篇内容:【有料干货】串扰测试方案(上篇)

2.>>>串扰的危害<<<

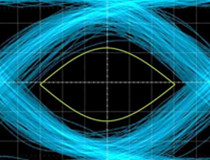

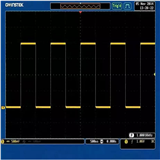

当耦合信号或串扰信号足够大时,接收串扰信号的信号线上就会出现信号完整性问题。串扰可能在受害线上引起尖峰脉冲,也能引起电路时延的改变。串扰会引起系统的不稳定,严重时甚至可能会引起系统的崩溃。下图是高速传输链路不同的位置的眼图测量。

在PCB设计中,如果处理不当,串扰对PCB的信号完整性将产生以下两种典型的影响。

由串扰引起的数字电路功能错误是电路设计中最为常见的一种。

串扰噪声导致电平逻辑错误

2.2串扰引起的时序延时

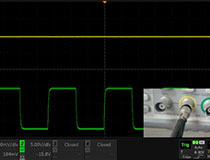

在数字系统设计中,时序问题是一个必须考虑的重要问题。下图显示了由串扰噪声引起的时序问题。图中下半部分是干扰线产生的噪声脉冲,当噪声脉冲叠加到被干扰信号上,就会造成被干扰网络信号传输延时减少。尽管这种减少网络传输延时的串扰噪声对改善 PCB 时序是有帮助的,但在实际 PCB设计中,由于干扰信号的不确定性,这种延时是无法控制的,因而对这种串扰对于电路设计造成严重的干扰,是需要避免的。

串扰噪声导致的信号传输延时

3.>>>串扰测量<<

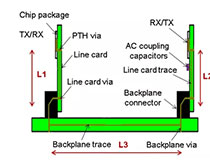

以往人们通常把印刷电路板、连接器、电缆和过孔当成是简单的部件,稍加考虑或者无需其他因素就可以很容易地把它们组成一个系统。现在,从逻辑电平0到逻辑电平1的数据上升时间30ps,如此高速的信号在传输线路上传输时会形成微波传输线效应,这些传输线效应对信号的影响会更加复杂。为了保证信号传输的质量,串扰测试成为了研发生产中不可缺少的环节。

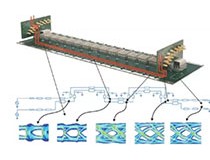

下图是一个针对串扰测试全面的方案设计图,能够支持串扰测试、眼图测试、误码测试、及阻抗测试。这里着重介绍串扰测试部分。

总体方案设计

中星联华科技(北京)有限公司的SL3000A插卡式高速串行误码仪能够通过可插拔模块同时具有串扰源产生、数据源产生、误码检测及比对等功能。

本系统特点:

1.支持NRZ/PAM4波形;

2.单通道码速率1-32GBd连续可调,支持生级至56GBd;

3. 支持同步/异步串扰;

3.上升下降时间:15ps(20%-80%)@28Gbps;

4.输出幅度:0.1Vpp-1Vpp,选件扩展最大幅度到4Vpp,选件扩展为直流输出,偏置电压-4V至+4V可调;

5.支持伪随机码型:PRBS7/9/10/13/15/23/31/64bit UDP;

6.触发时钟输出支持码速率2/4/8/16分频比可调;

8.支持内部精准时基,频率稳定度≤±0.05ppm,支持内外时基自动切换;

9.可以调节频率精度至±0.1ppm。