为这项分析所选择的PWM控制器具有一个0.26V的反馈基准电压。所以,LED电流为1A时,LED感测电阻器的功率耗散只有0.26W。由于CSM具有值为50的增益,就需要一个小很多的感测电阻器来感测输出电流。当流经CSM分流电阻器的电流超过CSM感测电阻器设定的限值时,CSM增益和比较器阀值 (R, R),PMOS导通晶体管中断负载电流—从而发挥电子断路器的作用。

可通过将RESET引脚切换为低电平来复位锁存输出。然而,考虑到这篇文章的目的,RESET已经被禁用,以检验响应速度。响应速度和峰值电流取决于很多变量。这些变量包括组件选择、CSM带宽、噪声滤波器、输出电容、FET选择、和输出升压电感器。这些因素和在一起会影响转换器的输出阻抗。为了准确评估运行方式,我们曾以50ns的最大时间步进和设定为0.001%的直流相对容限运行仿真。此分析在TINA-TI,一款免费的Berkeley SPICE 3f5兼容仿真器中运行。工作频率300kHz的升压转换器的5ms仿真在仅仅30秒以内即可启动至稳定状态。

将CSM放置在何处

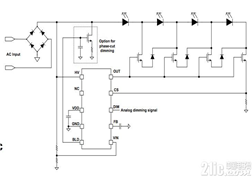

CSM可被放置在升压转换器的输入或输出上。在这个模拟中,CSM被放置在输出上,它通过与输出PMOS导通元件 (T5) 相并联的10 mΩ分流电阻器来感测电流。根据CSM的放置位置,此电路可以防止内部和/或外部短路情况。然而,CSM必须被设计成在所有工作条件下均具有足够共模范围 (CMR)。

如果放置在升压转换器的输入上,可选择具有较低CMR的CSM。然而,将CSM放置在输出上可以避开升压电感器,并且有助于加快对短路情况的反应时间。无论将CSM放置在何处,都应该使用一个RC滤波器来衰减那些会由于分流电阻器的突然di/dt事件而出现的噪声和谐振振铃。一个小型100电阻器和差分电容器可被置入比估计的分流器Lp/R时间常量大3倍的时间常量,其中Lp是寄生并联电感。由于CSM的增益误差和带宽受到噪声滤波器的负面影响,保持滤波器的低值很重要。

模拟结果

图5展示了模拟结果。Vg是到PMOS FET的控制电压,并在正常情况下被设定为-6V。需要根据FET的阀值电压、栅极电荷、和饱和特性进行优化。最大限度地减小栅极上的电压可以改进反应时间,并且应该选择上拉电阻器来尽可能地缩短中断周期。需要注意的是,输入电流和栅极电压用高栅极电荷(紫色),和低栅极电荷(蓝色)MOSFET显示。