由于短沟道效应,Sub-5 nm硅(Si)基场效应晶体管的制造是非常困难的。随着沟道长度的减小,CMOS器件不仅受到小尺寸的制造技术的限制,而且还受到一些基本的物理学原理如漏电场、电介质的击穿等限制。为了突破5纳米节点晶体管的限制,研究人员探索研究了基于碳纳米管、半导体纳米线以及二维过渡金属化合物等材料的场效应晶体管,但这些器件的工作仍然依赖于外部栅极电压的调控机制。如果这种情况不能继续下去,这可能意味着摩尔定律的终结。

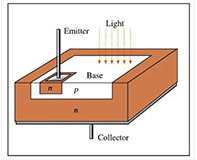

中国科学院外籍院士、中国科学院北京纳米能源与系统研究所首席科学家王中林,于2006年利用氧化锌纳米线受应力时,产生的压电电势来调控场效应晶体管的载流子输运特性,即后来所说的压电电子学晶体管,并且首次提出了压电电子学的概念。压电电子学晶体管是一种利用完全不同于传统CMOS器件工作原理的新型器件。这种器件利用金属-压电半导体界面处产生的压电极化电荷(即压电电势),作为栅极电压来调控晶体管中载流子的输运特性,并且已经在具有纤锌矿结构的压电半导体材料中得到了广泛证实。这种具有二端结构的晶体管不仅创新地利用界面调控替代了传统的外部沟道调控,并且有可能打破沟道宽度的限制。

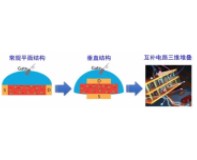

近日,在王中林和西安电子科技大学教授秦勇的指导下,王龙飞、刘书海和殷鑫等制备了一种新型的、沟道只有~2 nm的超薄氧化锌压电电子学晶体管,首次将压电电子学效应引入到二维超薄非层状压电半导体材料中。该工作系统地研究了二维超薄氧化锌垂直方向上的压电特性,利用金属-半导体界面处产生的压电极化电荷(即垂直方向上的压电电势)作为栅极电压有效地调控了该器件的载流子输运特性,并且通过将两个超薄压电电子学晶体管串联实现了简易的压力调控的逻辑电路。这项研究证实了压电极化电荷在超短沟道中“门控”效应的有效性,该器件不需要外部栅电极或任何其它在纳米级长度下具有挑战性的图案化工艺设计。这项研究成果开辟了压电电子学效应在二维非层状压电半导体材料的研究,并且在人机界面、能源收集和纳米机电系统等领域具有潜在的应用前景。

相关研究成果以Ultrathin Piezotronic Transistors with 2 nm Channel Lengths 为题发表在ACS Nano上 (DOI: 10.1021/acsnano.8b01957)。