挑战1:串扰(Crosstalk)

DDR信号较多,走线较为密集,随着信号速率的增加,传输线之间的串扰也会随之增加。此外,DDR颗粒的引脚布局,往往多个信号附近只有一个GND引脚,这就使得这些信号需要共用同一个返回路径,更加增加了相互干扰的风险。

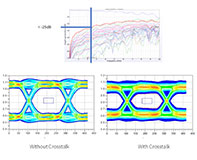

在图中不难发现,单一传输线之间的串扰都在-25dB以下,这个是相对不错的结果。然而,即使如此,在观察眼图时可以发现,串扰较为严重地减小了眼图地张开程度。这就意味着,单独从单一传输线的串扰角度上,并不能确切的得到串扰真实造成的影响,这给设计过程中,带来了困难。

挑战2:抖动(Jitter)

除了串扰外,抖动也是不能被忽视的问题。

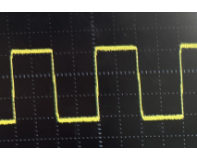

在上图可以看到,仅仅考虑随机抖动后,眼图的时间裕量就减小47%(27ps)。这意味着,如果忽视了抖动的影响,很容易对设计的质量的评估过优,最后造成实际产品的失败。

挑战3:码间干扰(ISI)及均衡(Equation)

由于传输线的频率选择特性,频率越高,传输线的插入损耗也会随之增加,信号的衰减和码间干扰的现象也会更加严重。

图中传输线在1.2GHz时插损约在-10dB左右,而上升到3.2GHz后,插损达到了-30dB。对比眼图可以发现,6.4Gbps时,由于ISI和衰减,眼图已经完全闭合。

为此,DDR5引入了可调增益以及判决反馈均衡器(DFE),减小ISI对相邻bit的影响,用以改善眼图闭合的情况。