图1 未经过滤波处理的开关信号

图2 延迟滤波程序流程图

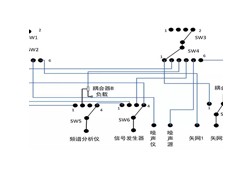

当检测到开关信号的状态发生变化时( 这里以由‘0’变到‘1’为例) ,计数器开始计时,当计数器的计数值计到N 时,如果开关信号仍保持为变化之后的状态‘1’,则输出‘1’,否则,认为这是一个干扰脉冲,将其滤除。当采样时钟的频率为5 kHz 时,TCLK = 0. 2 ms,要实现2 ms 的延时时间,若计数器初始值为0,那么计数器模值N = 9。具体的 VHDL语言 程序进程如下:

1. 3 延时滤波程序仿真

分别将开关信号din 设置成理想信号和抖动信号,利用QuartusⅡ8. 0 软件进行仿真,图3 和图4 分别为理想信号和抖动信号的延时滤波仿真波形图。