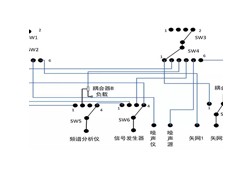

如上述过程,寄存器内的数据在不断地更新,数据每滑动一次,即对n 个采样值进行一次判断,从而达到滤波的目的。由于干扰脉冲的随机性,采到高电平和低电平的概率是相等的,所以,作为判断依据的百分比X 不能小于50%。在实际应用中,为了使滤波更可靠,X 的取值一般都大于50%。

2. 1 判决滤波程序设计

本设计采用一个9 位寄存器( n = 9) ,每次判断时只要‘1’的个数大于或等于5,则滤波输出‘1’,否则输出‘0’( X = 5 /9) 。图7 为判决滤波程序的流程图。

图7 判决滤波程序流程图

主要的程序进程如下: