然而,SoC 并非只有优点,要设计一颗 SoC 需要相当多的技术配合。IC 晶片各自封装时,各有封装外部保护,且 IC 与 IC 间的距离较远,比较不会发生交互干扰的情形。但是,当将所有 IC 都包装在一起时,就是噩梦的开始。IC 设计厂要从原先的单纯设计 IC,变成瞭解并整合各个功能的 IC,增加工程师的工作量。此外,也会遇到很多的状况,像是通讯晶片的高频讯号可能会影响其他功能的 IC 等情形。

此外,SoC 还需要获得其他厂商的 IP(intellectual property)授权,才能将别人设计好的元件放到 SoC 中。因为制作 SoC 需要获得整颗 IC 的设计细节,才能做成完整的光罩,这同时也增加了 SoC 的设计成本。或许会有人质疑何不自己设计一颗就好了呢?因为设计各种 IC 需要大量和该 IC 相关的知识,只有像 Apple 这样多金的企业,才有预算能从各知名企业挖角顶尖工程师,以设计一颗全新的 IC,透过合作授权还是比自行研发划算多了。

折衷方案,SiP 现身

作为替代方案,SiP 跃上整合晶片的舞台。和 SoC 不同,它是购买各家的 IC,在最后一次封装这些 IC,如此便少了 IP 授权这一步,大幅减少设计成本。此外,因为它们是各自独立的 IC,彼此的干扰程度大幅下降。

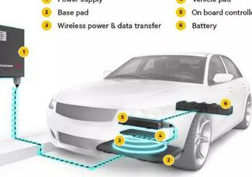

▲ Apple Watch 采用 SiP 技术将整个电脑架构封装成一颗晶片,不单满足期望的效能还缩小体积,让手表有更多的空间放电池。(Source:Apple 官网)

采用 SiP 技术的产品,最着名的非 Apple Watch 莫属。因为 Watch 的内部空间太小,它无法采用传统的技术,SoC 的设计成本又太高,SiP 成了首要之选。藉由 SiP 技术,不单可缩小体积,还可拉近各个 IC 间的距离,成为可行的折衷方案。下图便是 Apple Watch 晶片的结构图,可以看到相当多的 IC 包含在其中。

▲ Apple Watch 中采用 SiP 封装的 S1 晶片内部配置图。(Source:chipworks)

完成封装后,便要进入测试的阶段,在这个阶段便要确认封装完的 IC 是否有正常的运作,正确无误之后便可出货给组装厂,做成我们所见的电子产品。至此,半导体产业便完成了整个生产的任务。