PAM4的CDR

以上是基于NRZ 的CDR的介绍,到了PAM4以后,时钟数据又怎么恢复的呢?PAM4 CDR相对于NRZ信号的CDR而言,其设计难度增大。但是其基本原理差不多,都是依据PLL实现时钟锁定。

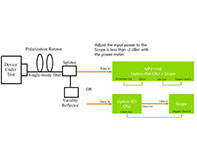

图6 PAM4 CDR结构

PAM4的时钟提取

1)串并转换,将25 GBaud的PAM4信号转成4路并行的6.25 GBaud PAM4信号,并行化的好处是降低每路的波特率(速率),让PLL更容易捕捉频率和相位,也会获得更好的抖动性能。

2)PD的核心部分是其前端电路 (PD-FE),它由并行的3 条数据通路和1条边沿通路构成,而每条通路均包含了1个判决器。PD-FE中除3位判决器之外通过一种新型的积分器,用来实现前述相邻数据的积分,并据此给出调节时钟相位的超前(DN) /滞后(UP)信号,进而控制锁相环路中的CP对环路滤波器(LPF)充放电流,闭环调节时钟相位。

CDR的测试应用

1、实际测试中为什么需要CDR?

通常测试光模块眼图或者BER时,需要一个时钟和被测光信号同步,才能进行眼图或者BER测试。前面介绍了CDR的基本原理,那么实际应用中为什么需要CDR呢?

标准定义:

Ethernet IEEE 802.3,Fibre Channel, 以及OIF-CEI协议里规定,测试抖动,眼高/眼宽必须使用时钟恢复;

测试场景需要:

针对NRZ测试方面,如果待测件环境无法提供时钟输出,此时则需要CDR从信号中来提取时钟;针对PAM4测试方面,特别是400G的光模块,成为业界关注的重点。当前400G主流的光模块,不论是400G-FR8/LR8还是400G-FR4/DR4的实现方式其电口侧都是8路53 Gbps PAM4信号。

对于400G-SR8/FR8/LR8等模块来说,光模块内部只是做CDR(时钟恢复)以及电/光或光/电转换,因此光口侧与电口侧一样,也是8路53 Gbps PAM4信号。此种情况测试光眼图BER,可以采用电口侧的时钟作为示波器的trigger(此时时钟和光信号是同步的),也可以CDR来提取时钟。

但是对于400G-DR4/FR4/LR4等模块来说,光模块内部还有Gearbox DSP芯片做了retime处理,把两路电口输入复用成一路信号再调制到光上,因此光口侧的速率是电口侧速率的2倍,即4路106 Gbps PAM4信号。此时电口侧和光口侧的时钟不同步,我们则必须要用一个外部的CDR来提取时钟,以便trigger和光信号同步,才能测试106 Gbps的光眼图。

图7 53G CR

2、CDR对测试的影响

a)Loop Bandwidth

PLL带宽选择越宽,信号越容易锁定,容忍信号的变化范围也大,但是输出的抖动也大;PLL带宽越窄,输出抖动越小,但是信号有变化时容易失锁。

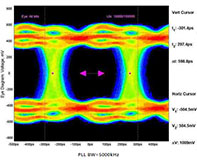

图8 不同BW的CR输出

b)输出抖动

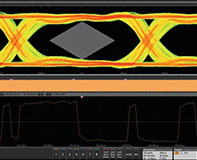

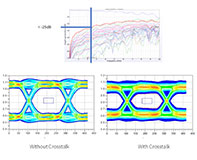

理想情况下PLL能及时追踪到数据跳变沿(即锁住相位),输出的时钟与输入数据同相,即抖动为零。实际情况中,当连续边沿的抖动变化太快时,PLL不能及时追踪到边沿的变化,于是恢复的时钟和数据边沿存在抖动,它的抖动传递函数(Jitter Transfer Function)的频响为高通滤波特性。这个抖动最终会传递到光眼图上,影响mask margin,TDEC/TDECQ等指标。TDECQ的测试中,对CDR的要求是环路带宽4MHz, slope 20dB/dec。

图9 抖动传递

总结

随着光通信的不断发展,PAM4技术的引入、数字芯片在光模块中的使用,以及后续的COBO/CPO封装的应用,在各种测试场景里,都需要使用到CDR以确保符合规范并进行准确的测试。

引用资料: 《面向5G通信的高速PAM4 信号时钟与数据恢复技术》