CDR的背景

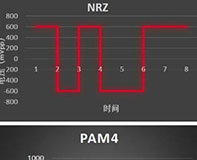

随着5G/数据中心的高速发展,光传输向着更高速率、更低延时演进,这就要求对应的光模块经过传输后尽量减小失真,以便在接收端将信号完整地再生出来。从10G长距到25G,再到50G/200G/400G PMA4,由于光纤传输链路线性/非线性效应,因此需要引入时钟数据恢复技术(CDR:Clock Data Recovery)。

CDR的原理

时钟恢复(CDR)的原理:

首先,利用本地产生的多相位时钟对数据多次采样,判断数据比特的边沿,并通过PLL将时钟边沿与其对齐,从而实现与数据同频率、同相位时钟的恢复。

其次,利用已同步时钟的最优相位对输入数据采样,使其实现最高的输入信噪比,并把采样结果作为已恢复数据输出。

时钟是数字通信的基础,在设备发射端,数据是根据时钟的节拍,一拍一拍拍出来的。同样在接收端,数据也是根据时钟的边沿(上升沿/下降沿)来采样获得的。

图1

如果没有时钟做标定,一连长串的数据没有意义,如上图,是101,还是110011?如何解决这个问题呢?

1)随路时钟(trigger), 不需要额外的时钟恢复,但是需要多一路时钟信道。

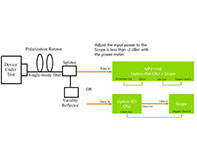

图2

2)时钟恢复,需要接收端具备时钟恢复的能力。那么如何从串行数据中提取时钟呢?

CDR结构组成

CDR核心--锁相环(PLL:Phase Lock Loop)

数据经过CDR恢复的时钟再生以后,变成理想信号,这个比较容易理解。重点就是这个时钟是怎么恢复出来的,这个也就是CDR的核心部分,即锁相环PLL。

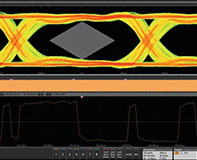

图3

锁相环有3个部分组成:鉴相器、低通滤波器、压控振荡器(VCO)。

鉴相器PD(Phase Detector/phase comparator)

图4 PD/CP示意图

经过鉴相器以后,频差(或者相差)再经过低通滤波器的积分,就以电压的形式控制VCO的输出频率。VCO(压控振荡器)是一个电压控制频率输出的器件。实质上这个过程就是一个电压反馈回路:

1)当时钟频率低于输入信号频率时,电压越来越大(PWM占空比增大,高电平占比增多),VCO输出频率提高,时钟加快;

2)当时钟频率高于输入信号时候,电压越来越小(PWM占空比减小,低电平占比增多),VCO输出频率减小,时钟减慢;

通过以上两个过程,实现动态平衡,最终VCO输出的频率锁定(等于)输入信号的频率。

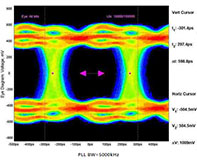

图5 频率相位锁定

上图DATA IN是理想的010101电平。但是实际上数据输入可能是11001100011100001111,有长连0,长连1的。那么此时该如何处理呢?

对于数字逻辑来说频率最快的是0101,如果出现了长连0或者长连1以后,我们可以理解为此刻信号的频率变低了:

经过鉴相后PD OUT有长高/长低电平,此时VCO频率会降低,时钟就会减慢;

时钟减慢后,此时PD OUT又出现了高电平,又需要将时钟变快,如此反复调节完成动态的平衡,最终时钟锁定。

我们知道锁相环里面的低通滤波器是个积分器,上面出现的有限的连0和连1,不会改变VCO的电压,因为积分器需要一定的时间才能引起VCO上电压的变化。如果连续的连0或者连1太多,将会导致VCO上的电压发生改变,就会引起失锁。